# Design Of Power Efficient 12T Sram Using Adiabatic Technique For Charge Recovery Application

J Sudhakar

MTech Student, Department Of ECE, VLSI System Design, Avanthi Institute of Engg. & Tech., India. Email: prasannavemuganti@gmail.com

Dr.S. Kishore Reddy

Associate professor, HOD, Department Of ECE, VLSI System Design, Avanthi Institute of Engg. & Tech., India. Email: kishorereddy416@gmail.com

G Srinivas

Assistant professor, Department Of ECE, VLSI System Design, Avanthi Institute of Engg. & Tech., India. Email: kishorereddy416@gmail.com

Abstract—As per the requirement of a design with minimal power has been a cardinal matter for the systems based on digital technology & greater performance like microprocessors, DSPs & various applications apart. The rise in market of mobile & electronic products powered by portable batteries needs chips which intake minimal power. SRAM incorporates around 60% of VLSI circuitries. Also memories are considered as the major flaw for decadence of power in a circuitry but no digital circuitry is accomplished by nor using memories. The absorption of power & SRAM's speed are major concern which followed several designs in accordance to the minimal absorption of power. The main concern of this document is on decadence of power while operation of Write is executed in 6-T CMOS SRAM. In this paper we mainly focus on decadence of power during short circuits also the fluctuating decadence of power which can also be termed as power which is dynamic. The tool of Tanner is deployed to evaluate the circuitry, the schema of cell of SRAM is formulated on S Edit & simulation of net list is furnished by making use of T Spice & also assessment of waveforms is done by W Edit.

*Index Terms*—Minimal Power, SRAM, 130nm, 7T SRAM cell

#### I. INTRODUCTION

A memory of semiconductor which is also ARAM is a bistate circuitry that is ployed to retain every single bit. The static & dynamic RAM which should be refreshed in a defined period of time. Reminisce is also explained by SRAM but it has volatile nature in a traditional way that means that data will not be retained if memory is turned off.

While commencing the particulars of design to formulation of layout of mask, the design of layout of an integral circuitry have various steps in processing which needed to be focused while execution. The steps invades design of schema at level of transistor, simulation of SPICE at circuitry as per designed proportions of W/L of a distinct transistor, formation of layout by making use of editor of layout, designing check rule, extraction in parasitic manner & exact evaluation & simulation. Such methodologies for processing can't be changed for operations which are free from error & same king of methodology is deployed for design of IC of SRAM of 1 kilobyte. The cell of SRAM is its main constituent which accumulates one bit of information ata time. The lines of bit that are common can be written & read over cell of SRAM. A standard tool for industry which is SPICE is ployed for purpose of simulation & assessment of cell of SRAM & eventually for complete design. The

Manuscript received Oct 10, 2022; Revised Oct 25, 2022; Accepted Nov 4, 2022

circuitry which is already charged, the amplifier of sense & circuitry of read & write accomplish memory of one SRAM. The arrangement of matrix is done in form of rows & columns that enhance the addressing of memory in an easy wayof bits of memory & also furnish flexibility in design. As the working of array of cells of memory is evaluated, its imitation can be done for various times by making fewer variations in design in regulatory circuitry of I/O.

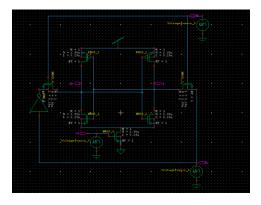

## A. Plan of the chip

The diagram of whole chip is presented in the Figure 1. There are 6 transistors that are arranged in 8 blocks. Each cell of SRAM can retain 1 kilobyte of information. There are address lines 10in number like from A0-A9 which are ployed to label the locations. From these A0, A1,A2 are taken as lines for decoding of address of column, and A3-A9 are used for purpose to decode rows. Every single row has 8 cells of memory & formulates a single byte. So the lines of address points to every byte but not bit.

There are 8 columns & 128 rows in every block. So total of 49,152 transistors, 8 blocks\* 128 rows \* 8 columns \* 6 transistors are there. The decoding of rows of every block is done by making use of decoder based on NOR as 7 \*128. There are 1024 transistors for this circuitry. The decoder of outcomes is linked to every row of block. Parallel every single block is chosen by a decoder of column of 3\*8. There are 32 transistors in total.

The amplifier of sense is ployed to sensation of information located in cell of memory. The blockof control for output & input information is comprised of circuitry for write & read in relation to circuits of driver. The data for 8 bits are from D0 to D7 is either written or read in parallel. The WE & RE are the lines of control that are furnished for chip. As by its name, RE is triggered before operation of read for the operations of reading. Just like to this, the WE signal is triggered for operations of write.

## B. SRAM cell: schematic and working

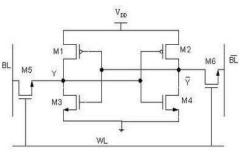

The figure presents memory cell of SRAM for an individual bit. The latches which are static are

deployed in cell of SRAM. The cell is formulated from a flip flop that is consisted of inverters which are coupled as cross. The transistors of access which are 2 in number are ployed to evaluate the information retained in cell. The line for control that is WL, word line turns the transistors OFF or ON. In general, the WL is linked to outcome of circuitry of decoder of row. As the WL is equal to Vdd, BL is linked to cell of SRAM & its complementary, which allows both write & read operations. The function of read & write is executed by transistors of access.

## C. Read operation:

The Y node is taken as the node for reference for cell of SRAM. As the node of Y at Vdd is high, value

#### Figure 1. Schema for cell of SRAM

1 is stored in cell & bar of Y node retains value 0. For the circumstances that have reverse voltage, cell retains value 0. It is taken that cell retains the value of 0. As the operation of read commences, the lines of BL & BL bar are charged to Vdd/2. As by the initiation of WL, the flow of current is by M5 & M6. Though current will flow through Vdd by M1 & M5 fluctuating the capacitance of line of bit, like Cbl. The present capacitance on line of BLbar like CBLbar dispenses the transistors by M6 & M4. The process formulates a difference in voltage among the node Y &Y bar which is detected by amplifier to sense value of 1. To parallel to this, value of 0 is sensed by amplifier.

## D. Write operation:

Here the operation to write value 0 is presumed to store 1 value. By this, amplifiers of sensing & circuitries which are pre charged are disabled. This cell is chosen by triggering the associating signal of WL. In order to write value of 0 to cell, line of BL is taken down to the line of BLbar, which is enhanced to Vdd

by the circuitry of write. So the Ybar node is raised to Vdd/2 eventually Y node is brought down to the same. As the voltage gets over the level on 2 node feedback, action commences. The capacitances are formulated by M4, M6 & M3, M5 which are discharged & charged consequentially. Eventually the Y node is made stable at 1 value. As the capacitances of parasitic are furnished by transistors, which has value much lesser than capacitance of line of bits, and operation of write works fast than read.

#### E. Transistor sizing:

The proportion of W/L is chosen to furnish the gate with the ability of driving in all directions that is in relation to a standard inverter. From a standard design of inverter, W/L value is 1.5 or 2for a relative design,  $(W/L)_p = (\mu_n/\mu_p)(W/L)_n$ . The cell of SRAM is formulated in a way that whilefunctioning of operation of read, variations in Ybar & Y are minimal in order to avert cell to varyits state. In general, 2 inverters which are coupled together of cell of SRAM are formulated like Kp & Kn are countered. The threshold is put at Vdd/2 at the place of design. The extent of transistors of access is formulated around 3 times greater in width to the inverter's Kn. In order to attain the optimal functioning of cell followed by proportion of W/L is selected for various transistors. Minimal proportion of 2 is needed for transistors of inverters of NMOS & 4 are mandatory for transistors of PMOS. Transistors of access are formulated by doubling the width or even more by furnishing a proportion of W/L greater than 4. Though the proportion of set don't get in accordance to the rule of design of Cadence Virtuoso editor of layout for technology of 0.18 micron. The minimal width for the transistor of NMOS is 0.6 micron for technology of 0.18 micron. So the proportion of W/L is 3.33. The proportion of PMOS will be 6.66. This leads to a width of 1.2 micron. On the formulation of simulation of SPICE are the assessments & outcomes, proportion of W/L is for transistor of access is retained at 9.99. This incorporates the width of gate of 1.8 micron.

#### II. EXISTING DESIGN DESCRIPTION

SRAM is basically a cell of memory in semiconductor. In accumulates a bit of data. it

functions fast & absorbs minimal power in contrast to other cells of memory. As it is robust & has much more stability, more improvisations are being done in cells of SRAM. SRAM is considered as a cardinal element on a microprocessor chip. Formulating a cell of SRAM on a nanoscale is formulated as a task that is challengeable as margins in noise are deduced & sensitivity has been raised to fluctuations in voltage of threshold. The cell of 10T-SRAM has better performance than6T-SRAM on the factors of stability & reliability. Cell of 6T-SRAM is not much reliable when supply of power is less because margins in noise get degraded.

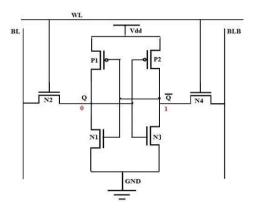

There are 6 transistors in a cell of 6T-SRAM. The figure presents a standard cell. The transistors for access are N2 & N3 and other 4 transistors, N1, N2, P1, P2 formulates 2 inverters. Information is latched by these 2 inverters. The information gets invaded to inverter of latching by transistor of access. The method to introduce information is termed as operation of writing & process to retrieve information is termed as process of reading. A row of cell of SRAM is chosen by WL. A column is chosen by BLbar & BL. A defined cell of SRAM is chosen as BL & WLare turned on. A 6T-SRAM & extra circuitry of reading can formulate cell of 10T-SRAM.

A cell of 10T-SRAM gets designed by making use of cadence virtuoso in technology of CMOS180mm & characteristics of the performance like delay, power, delay in power areassessed.

Figure 2. A 6T cell of SRAMs

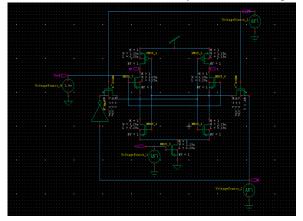

## A. Design And Simulation Of A 10t Sram Cell

Architecture of cell of 10T-SRAM is alike to cell of SRAM of 6T, but difference is that it has an extra circuitry for read. Figure 2 presents cell of SRAM designed for 10T. In cell of 10T-SRAM, 10 transistors are ployed. It comprise of traditional cells of 6T-SRAM & extra circuitry to read. The issue arises in traditional cells of 6T-SRAM is that there are chances to data to be lost while execution of operation of read. Flipping can occur at voltage at node at Q & Qbar because of inverters aligned back to back.

This problem can be eliminated by putting an additional circuitry. The operations of read in 6T and 10T-SRAM cells are similar. While in scenario of operation of reading, sharing of charges occurs in RBL

& no-transformed BL-BLB while operation of read is executed. As charge are shared, so lines of reading bit don't get discharged fully & remains at a mid level of voltage. Thus, working of cell becomes like an automated limiter for swinging lines of bit.

Figure 3. Design of a 10T SRAM cell

#### III. PROPOSED METHODOLOGY

#### A. PROPOSED 7T SRAM CELL

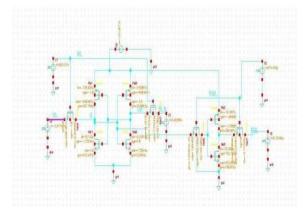

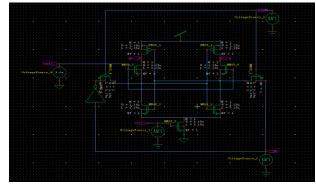

The given Figure 5 presents schema of cell of SRAM with less power & signals related to it wherever, CS, WL are required for making a selection for writing & data can be written from bit bar & bar.

As represented by Figure . cell with minimal power is comprised of an additional transistor & gate of that

Figure 4. Suggested Circuitry

additional transistor will regulate operation of reading or writing information & also when operation of write is executed as the additional transistor cuts down the path in Vdd & ground & save circuitry from short circuit. We can make use of input, bit data or its complementary to execute operation of writing.

Functioning of cell of SRAM with less power & operation is explained in the modes of write & read as below:

#### A. Read Mode

Generally, cell of SRAM with less power in mode of reading is alike to traditional cell of SRAM. In this mode, value 1 is assigned to CS & an additional transistor will be activated on the basic operation of reading for cell of SRAM when a high voltage is provided to WLs, both the transistors of access will get activated & data needed will be out by the sensing amplifier.

#### B. Write Mode

In mode of writing, node of B should be assigned higher value which is achieved by putting CS as 0 invading signals of WL value of data is implemented to BL. There may be a possibility to write state of cell from 1 to 1. As bodes of B & CS, both are 0, no transition in state occurs. As conductance of N4 transistor has greater conductance than P2, the state of cell is flipped easily from 0 to 1 as node B is discharged by N4. As data can be written from 0 to the corresponding path as presented in figure .

International Journal of Engineering Innovations in Advanced Technology ISSN: 2582-1431 (Online), Volume-4 Issue-4, December 2022

Figure 5. 6T traditional circuitry

IV. RESULTS

## A. 6T Conventional Circuit

In this circuitry, we deploy transistors 6 in numbers. BL & WL is defined for write & readoperations. The absorption of power for figure 6.1 is 7.028097e-006 W & delay is 1.34ns.

Figure 6. Waveform of 6T traditional circuitry

B. PROPOSED 7T SRAM DESIGN

The absorption of power for design of 7T SRAM is 4.184023e-006W with delay of 840.06ps.

Figure 7. Suggested Circuitry

Figure 8. Outcome of waveform for suggested 7T SRAM

# V. CONCLUSION

As observations from outcomes reveal that in cells of SRAAM with less power, aggregated power gets brought down by 43%. It presents that cell of memory will absorb low power in contrast to traditional cells of SRAM whose outcomes are imitated in this document. In a situation of power with short circuits, decadence of power gets down by 43% that is less in contrast to traditional cells of SRAM. Thus, the cell of SRAM which is newly formulated absorbs low power & it can be said that it is aware of power that can be accepted in the present market of VLSI. The delay is also improvised by 74%. So, cell of SRAM absorbs low power & executes operation faster than a standard cell of SRAM. In this cell lesser amount of power s taken in & so it saves around 43% of power in contrast to the present cells of SRAM. Thus these cells are deployed in electronics which are portable & are operated by battery & so will need lowcost sink of heat to furnish heat to surroundings.

## VI. FUTURE SCOPE

This documentation can be elaborated for future work in order to bring down need of area that is around 16.72 % greater than the present cell of SRAM. A methodology can be searched to reduce this area & also there are no improvisations in cells of low power when operation to write1 is executed& so work can be extended for improvisation in delay whenever, operation of writing is executed.

## REFERENCE

- [1] Shunji Nakata, Hiroki Hanazono, Hiroshi Makino, Hiroki Morimura, Masayuki Miyama, and Yoshio Matsuda" Increase in Read Noise Margin of Single-Bit-Line SRAM Using Adiabatic Change of Word Line Voltage" IEEE Trans. Very Large Scale Integr. (VLSI) Syst., vol. 22, no. 3, March 2014.

- [2] Ho, K. Iniewski, S. Kasnavi, A. Ivanov, and S. Natarajan, "Ultra-low power 90 nm 6T SRAM cell for wireless sensor network application,"in Proc. IEEE Int. Symp. Circuits Syst. , May 2006, pp. 4131–4134.

- [3] S. R. Singh and K. Moez, "Ultra-low leakage 90 nm content addressable memory design for wireless sensor network applications," inProc. IEEE Int. Midwest Symp. Circuits Syst., Aug. 2009, pp. 1191–1194.

- [4] Frustaci, P. Corsonello, S. Perri, and G. Cocorullo, "Techniques for leakage energy reduction in deep sub micrometer cache memories, "IEEE Trans. Very Large Scale Integr. (VLSI) Syst., vol. 14, no. 11,pp. 1238–1249, Nov. 2006.

- [5] L. Chang, D. M. Fried, J. Hergenro ther, J. W. Sleight, R. H. Dennard. K. Montoye, L. Sekaric, S. J. McNab, A. W. Topol, C. D. Adams, K. W. Guarini, and W. Haensch, "Stable SRAM cell design for the 32 nm node and beyond," in Proc. Symp. VLSI Technol. , Jun. 2005, pp. 128–129.

- [6] S. Ohbayashi, M. Yabuuchi, K. Nii, Y. Tsukamoto, S. Imaoka, Y. Oda, M. Igarashi, M. Takeuchi, H. Kawashima, H. Makino, Y. Yamaguchi, K. Tsukamoto, M. Inuishi, K. Ishibashi, and H. Shinohara, "A 65-nm SoC embedded 6T-SRAM design for manufacturing with read and write cell stabilizing circuits," in Proc. Symp. VLSI Circuits, 2006, pp. 17–18.

- [7] S. Nakata, H. Suzuki, H. Maki no, S. Mutoh, M. Miyama, and Y. Mat-suda, "Increasing static noise margin of single-bit-line SRAM by lowering bit-line voltage during reading," in Proc. IEEE Int. Midwest Symp. Circuits Syst., Aug. 2011, pp. 1–4.

- [8] Koushik K. Das and Richard B. Brown, "Ultra Low-Leakage Power Strategies for Sub-1 V VLSI: Novel Circuit Styles and Design Methodologies for Partially Depleted Silicon-On-Insulator (PD-SOI) CMOS Technology" International Conference on VLSI Design, July 2003.

- [9] Blotti and R. Saletti, "Ultralow-power adiabatic circuit semi-custom design," IEEE Trans. Very Large Scale Integr. (VLSI) Syst. , vol. 12, no. 11, pp. 1248–1253, Nov. 2004.

- [10] S. Kim and M. C. Papaefthymiou, "True single-phase adiabatic circuitry," IEEE Trans. Very Large Scale Integr. (VLSI) Syst. , vol. 9, no. 1, pp. 52–63, Feb. 2001.