# Design of Seven Level Cascaded H Bridge Multilevel Inverter for Traction Applications

Jibilikapally Suman

Asst.Prof, Department of EEE, Anurag Engineering College (AUTONOMOUS), kodad, India. Email-Id: sumanjibilikapally@gmail.com

#### Badisa Sreenu

Asst.Prof, Department of EEE, Anurag Engineering College (AUTONOMOUS), kodad, India. Email Id: srinueee@anurag.ac.in

Abstract: Multilevel inverters are the circuit, which converters the input DC into AC. There are several types of multilevel inverters. Conventionally they are classified as diode clamped multilevel inverters, flying capacitor multilevel inverters, and cascaded H bridge type multilevel inverters. In these inverters, the output voltage quality is a very important parameter as the inverter performance will be decided by the same parameter. The output voltage quality is measured using the total harmonic distortion. The total harmonic distortion in a multilevel inverter depends on the inverter topology and the type of modulation or control method that is employed in a multilevel inverter. There are several types of modulation methods that can be applied to multilevel inverters. Some methods are general, which can be applied to all the inverters, and some of those methods are specifically designed for particular topologies only. Out of all the modulation methods, the unique feature of the selective harmonic elimination method is, it can remove or suppress the selected lower order harmonics from the output waveform of the multilevel inverter.

Index Terms: Voltage Quality, Inverter, Modulation, Harmonic Distortion,

# 1 INTRODUCTION

For most of the applications, the sinusoidal form of the output voltage is required for the smooth operation of the loads such as motors, etc. Using a conventional two-level inverter it is not possible to obtain the exact sinusoidal voltage at the load terminals of the multilevel inverter. Hence, the usage of conventional two-level inverters is not much in use for several applications due to the poor quality of the output waveforms.

inverters are proposed. Those multilevel inverters convert DC into near sinusoidal voltage waveform. The output voltage waveform of the multilevel inverters is very near to the sine wave.

To obtain the good quality of the output voltages, multilevel

## A Multilevel Inverters

There are several advantages to the usage of multilevel inverters when compared with the two-level inverters. Following are the major advantages of multilevel inverters.

- Reduced voltage stress

- Improve voltage/Power quality

- Low Electromagnetic interference.

- Low-frequency operation.

- Can be used for High power applications also.

Due to the above advantages, multilevel inverters are preferred compared to any other circuits in DC to AC conversion systems.

#### II LITERATURE REVIEW

The multilevel inverter is an emerging topic for research throughout the world for engineers and researchers. Millions of people are working on multilevel inverters on the globe. There are various issues related to the inverter. Most of the issues are highlighted in the literature.

Following are the various aspects that are having extensive references related to the multilevel inverters.

- Topological development of the various advanced inverters.

- Binary inverters.

Manuscript received April 05, 2022; Revised May 05, 2022; Accepted May 19, 2022

- Trinary inverters.

- Generalized inverters.

- Operation at high frequency.

- Operation at low frequency.

- Operation at mixed frequency.

- Reduction of stress on switches.

- Gate driver circuit design.

The list of several important papers related to the above aspects is given in the reference section. Those references will give a good insight into the various technological developments in the area of the multilevel inverter.

Many papers are available on the modulation strategies of a multilevel inverter. The work presented in this project is unique due to its specialty in eliminating the lower order harmonic reduction from the output voltage waveform using a novel method.

#### III CASCADED H BRIDGE INVERTERS

## A Introduction

Various aspects that are related to the cascaded H bridge inverters are presented in this chapter. Those inverters are compared with the other conventional multilevel inverter to show their effectiveness of those inverters. The comparison will give good insight for the reader in understanding the various issues of the multilevel inverters.

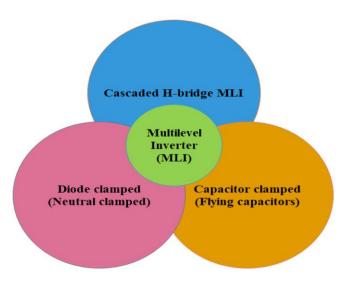

Figure 1: Conventional inverters

## B Type of Multilevel inverter

Conventionally, the following are the various types of multilevel inverters. The classification is also shown in the above figure.

- Diode clamped multilevel inverters

- Flying capacitor multilevel inverters

- Cascaded H bridge multilevel inverters.

The diode clamped inverters are also called the neutral clamped, the other name of the flying capacitor multilevel inverters is the capacitor clamped inverters.

# IV SELECTIVE HARMONIC ELIMINATION METHOD

#### A Introduction

In this chapter, various modulation methods that are suitable for the cascaded H Bridge inverter are presented. More emphasis is given to the selective harmonic elimination method, which is under consideration for the cascaded H bridge inverter topology.

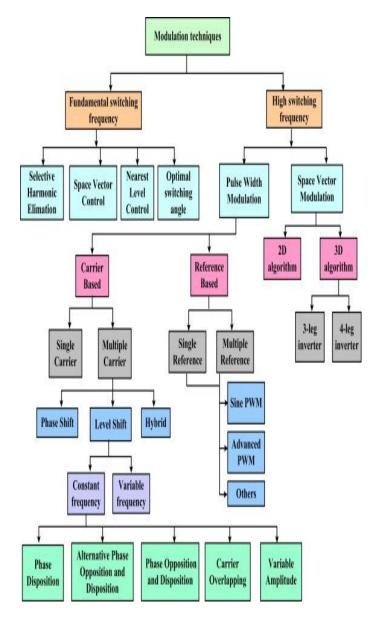

### **B** Modulation Methods

Following are the various modulation methods that are used for multilevel inverter topologies.

- ➤ High-frequency Methods

- Space vector control

- Sinusoidal pulse width modulation

- Carrier-based modulation.

- Low-frequency Modulation

- Space vector control

- Nearest level modulation.

- Angle calculation

- Selective harmonic elimination.

- Hybrid Modulation

- Mixed frequency modulation.

The detailed lists of various methods are summarized in the table shown below.

Table 1: Classification of Modulation methods for MLI.

## V SIMULATION RESULTS

#### A Introduction:

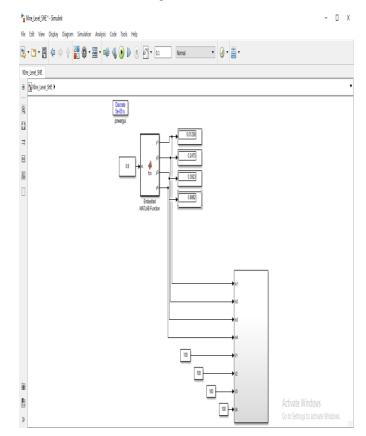

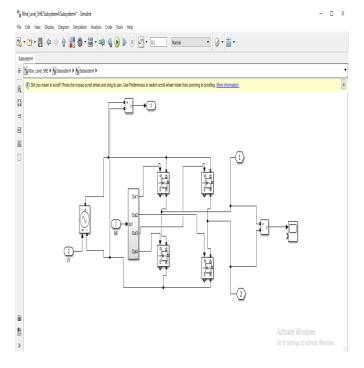

In this chapter, the implementation of the selective harmonic elimination is carried out for the cascaded H bridge

multilevel inverter. All the simulations are performed in MATLAB/SIMULINK.

### B Multilevel Inverter Specifications:

Following are the specifications of the multilevel inverter circuit, which is designed in MATLAB/SIMULINK in this work.

- Type of inverter: 9 level cascade H-bridge Inverter.

- DC source Value = 100 Volt

- Number of DC sources: 4

- Load Resistance Value = 100 ohm

- Modulation Index = 0.8

- The method used to solve the nonlinear equations is = Newton Raphson

- Harmonics Eliminated = 3<sup>rd</sup> order, 5<sup>th</sup> order, and 7<sup>th</sup> order.

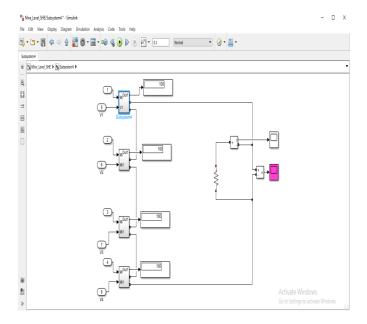

The simulation circuit consists of various blocks. Which, consists of DC sources, H bridges, Loads, and gating pulses, etc. The simulation diagrams are shown below for the multilevel cascaded H bridge inverter using the selective harmonic elimination/mitigation method.

Figure 2: Simulation Diagram of CHMLI using SHE.

Figure 3: Four H bridges connected in Cascaded mode.

Figure 4: H bridges Circuit subsystem.

# C Circuit Description

A 9 level H bridge inverter is simulated. It consists of 4 H Bridges connected in a cascade. Each H Bridge can generate

one positive voltage level, one negative voltage level, and a ZERO voltage level.

The resistive load is used in the simulation as the interest is only the removal of lower-order harmonic components in the output voltage waveform. Following waveforms are shown.

- Load Voltage waveform

- > FFT of the load voltage waveform

- ➤ Load current waveform

- > FFT of the load current waveform.

## D Output waveforms

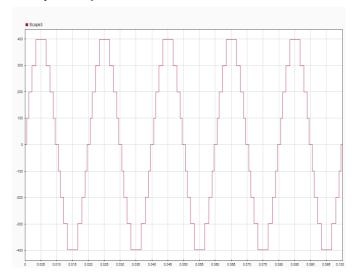

Figure 5:Output voltage Waveform of a 9 level inverter

The above waveform is the output voltage obtained using 9 level inverter with resistive load. It consists of four positive levels, four negative levels, and a zero level. The peak to peak voltage is 800, and the peak voltage is 400 volts.

The above diagram shows the FFT analysis of the output voltage obtained by the cascaded 9 level inverter using the Harmonic elimination method. The following things can be noted from the above diagram.

- > The magnitude of the fundamental voltage is high

- ➤ The magnitude of the 3<sup>rd</sup>, 5<sup>th</sup>, and 7<sup>th</sup> order harmonics is very low and they are suppressed successfully.

- > SHE method successfully eliminates the lower order harmonics.

- > RMS value of the output voltage is high.

- The THD of the output voltage is low (improved).

- ➤ The quality of the output voltage is improved.

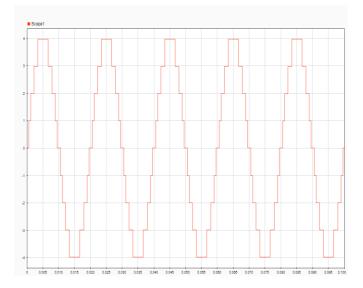

Figure 6: Output current Waveform of a 9 level inverter

The above waveform is the output current obtained using 9 level inverter with resistive load. It consists of four positive levels, four negative levels, and a zero level. The peak to peak voltage is 8 A, and the peak voltage is 400 ampere.

As the load is resistive, the output current is in phase with the voltage that is obtained using the multilevel inverter. The current is the scaling of the voltage waveform. To know the quality of the current waveform, we have to perform the FFT analysis for the current waveform also.

The above diagram shows the FFT analysis of the output current obtained by the cascaded 9 level inverter using the Harmonic elimination method. The following things can be noted from the above diagram.

- The magnitude of the fundamental component of current is high

- The magnitude of the 3<sup>rd</sup>, 5<sup>th</sup>, and 7<sup>th</sup> order harmonics is very low and they are suppressed successfully.

- > SHE method successfully eliminates the lower order harmonics in the current waveform too.

- > RMS value of the output current is high.

➤ The THD of the output current is improved.

The following table gives the summary of the entire work that is carried out in this report. The objective is to remove the lower-order harmonics from the output voltage of a cascaded multi-level inverter using the selective harmonic elimination method.

From the below table, it is clear that the SHE method successfully

- ➤ Eliminated the 3<sup>rd</sup> order, 5<sup>th</sup> order, and 7<sup>th</sup> order harmonics.

- > The RMS value of the fundamental component is improved.

- The THD of the voltage is improved alot.

- ➤ The improvement in THD results in the increased power conversion efficiency of the multilevel inverter.

Table 2:Summary of Simulation Results for output voltage

| S.No | Method         | THD<br>(%) | Fundamental (RMS) | 3 <sup>rd</sup> | 5 <sup>th</sup> | 7 <sup>th</sup> |

|------|----------------|------------|-------------------|-----------------|-----------------|-----------------|

| 1    | Without<br>SHE | 19.95      | 216.5             | 18.59           | 9.76            | 4.05            |

| 2    | With<br>SHE    | 9.63       | 285.8             | 0.4             | 0.3             | 0.01            |

# **CONCLUSION**

In this work, the following things are done to achieve the objectives that are defined in chapter 1. The major conclusions of the present work are

- A 9 Level cascaded H bridge inverter is simulated.

- A selective Harmonic Mitigation scheme is employed in the inverter.

- The Newton Raphson method is used in solving the system equations.

- The output voltage and current are obtained.

- FFT analysis is performed for both current and voltage.

• From the results, it is shown that the SHE method successfully eliminated the lower order harmonics, improved the fundamental voltage, and improved total harmonic distortion (THD).

## **FUTURE SCOPE**

There are several aspects to discuss the selective harmonic elimination. In this work, only a few aspects are discussed and presented. Some aspects are not presented, which are left as the future scope of this project.

Following are the future scope of this project

- Analysis of various algorithms for SHE.

- Implementation of SHE with high switching frequency.

- Generalized formation for any waveform.

- Applications to the machine drive system.

#### REFERENCES

- 1.Krishna, R.theA.; Suresh, L.P. A Brief Review on Multi-Level Inverter Topologies. In Proceedings of 2016 International Conference on Circuit, Power and Computing Technologies (ICCPCT), Nagercoil, India,18–19 March 2016; pp. 1–6.

- 2. Babaei, E.; Kangarlu, M.F.; Maziar, F.N. Symmetric and asymmetric multilevel inverter topologies withreduced switching devices. Electr. Power Syst. Res. **2012**, 86, 122–130.

- 3. Babaei, E. A Cascade Multilevel Converter Topology With Reduced Number of Switches. IEEE Trans. PowerElectron.**2008**, 23, 2657–2664.

- 4. Ahmed, R.A.; Ping, H.W. New multilevel inverter topology with a minimum number of switches.In Proceedings of the TENCON 2010—2010 IEEE Region 10 Conference, Fukuoka, Japan, 21–24 November 2010; pp. 1862–1867.

- 5. Umashankar, S.; Sreedevi, T.S.; Nithya, V.G.; Vijayakumar, D. A New 7-Level Symmetric Multilevel Inverterwith Minimum Number of Switches.ISRN Electron. 2013, 2013, 476876.

- 6. Veenstra, M.; Rufer, A.; Member, S. Control of a Hybrid Asymmetric Multilevel Inverter for CompetitiveMedium-Voltage Industrial Drives. IEEE Trans. Ind. Appl. **2005**, 41, 655–664.

- 7. Ceglia, G.; Guzmán, V.; Sánchez, C.; Ibáñez, F.;Walter, J.; Giménez, M.I. A New Simplified Multilevel InverterTopology for DC—AC Conversion.IEEE Trans. Power Electron.**2006**, 21, 1311–1319.

- 8. Najafi, E.; Halim, A.; Yatim, M.; Member, S. Design and Implementation of a New Multilevel InverterTopology. IEEE Trans. Ind. Electron. **2012**, 59, 4148–4154.

- 9. PoyyamaniSunddararaj, S.; Rangarajan, S.S.; Gopalan, S. Neoteric Fuzzy Control Stratagem and Design of Chopper fed Multilevel Inverter for Enhanced Voltage Output Involving Plug-In Electric Vehicle (PEV)Applications. Electronics **2019**, 8, 1092.

10. Rangarajan, S.S.; Collins, E.R.; Fox, J.C. Smart PV and Smart Park inverters as suppressors of TOVphenomenonin distribution systems. IET Gener.Transm.Distrib.**2018**, 12, 5909–5917.

#### AUTHORS PROFILE

Jibilikapally Suman working as an assistant professor in department of EEE, Anurag Engineering College (Autonomous), Ananthagiri, Kodad. He obtained B. Tech (Electrical and Electronics Engineering) and M. Tech (Electrical Power Systems) degrees

from JNTU-HYD in 2012 and 2016 respectively. He has more than 5 years experience in teaching experience.

Badisa sreenu working as an assistant professor in department of EEE, Anurag Engineering College (Autonomous), Ananthagiri, Kodad. He obtained B. Tech (Electrical and Electronics Engineering) and M. Tech (Power electronics) degrees from

JNTU-HYD in 2005 and 2012 respectively. He has more than 5 years' experience in teaching experience.